### 200 Msps, 16-/14-Bit Low-Power ADC with 8-Channel MUX

### Features:

- · Sample Rates:

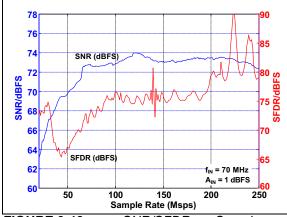

- 200 Msps for single-channel mode

- 200 Msps/Number of channel used

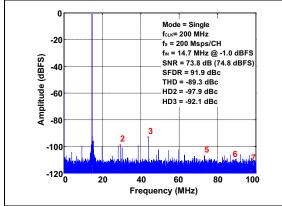

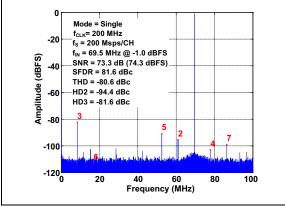

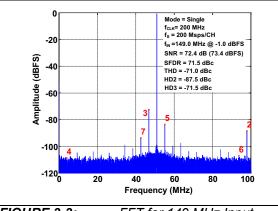

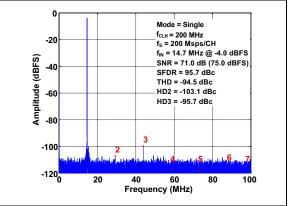

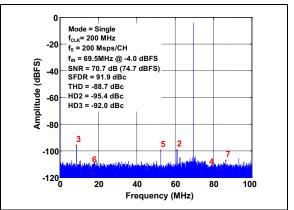

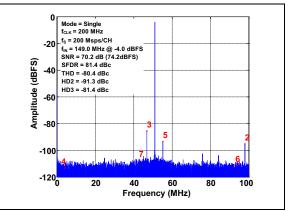

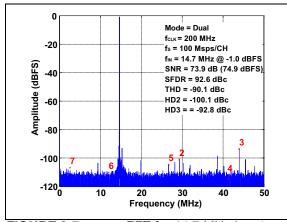

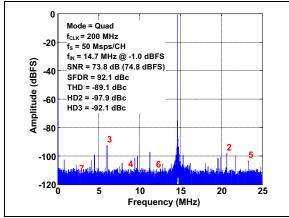

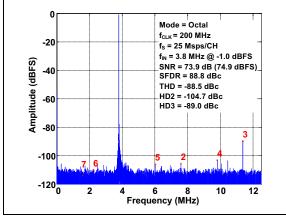

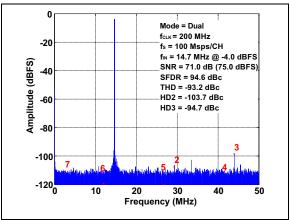

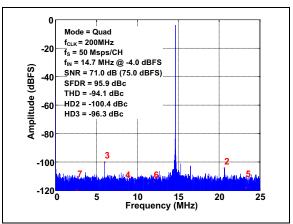

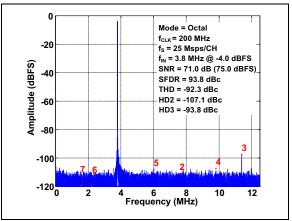

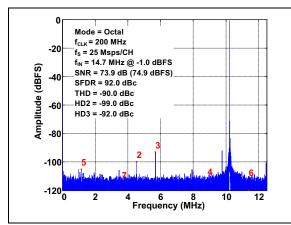

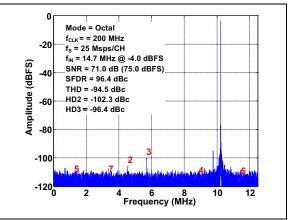

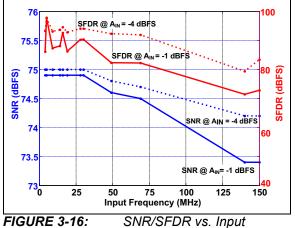

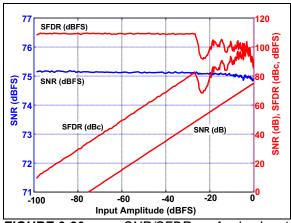

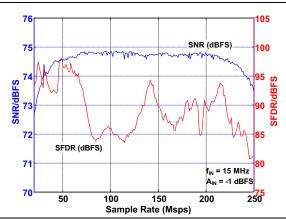

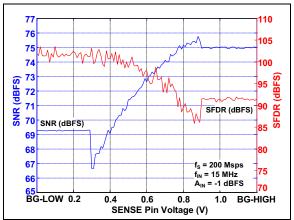

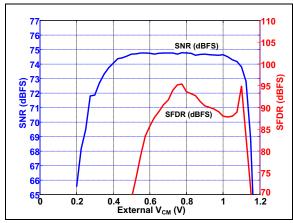

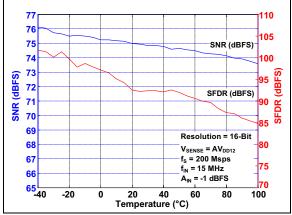

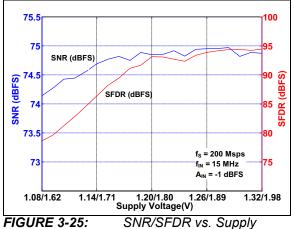

- SNR with f<sub>IN</sub> = 15 MHz and -1 dBFS:

>74 dBFS for 200 Msps

- SFDR with f<sub>IN</sub> = 15 MHz and -1 dBFS:

- >90 dBFS at 200 Msps

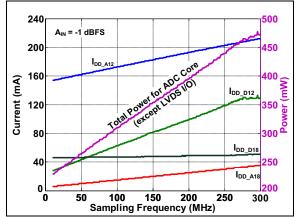

- Power Dissipation with LVDS Digital I/O:

- 490 mW for 200 Msps

- Power Dissipation with CMOS Digital I/O:

- 436 mW for 200 Msps, Output Clock = 100 MHz

- Power Dissipation Excluding Digital I/O:

- 390 mW for 200 Msps

- Power Saving Modes:

- 80 mW during Standby

- 33 mW during Shutdown

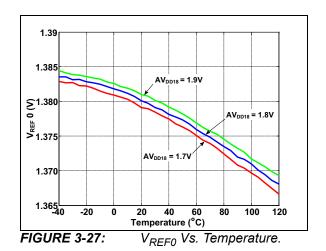

- · Supply Voltage:

- Digital Section: 1.2V, 1.8V

- Analog Section: 1.2V, 1.8V

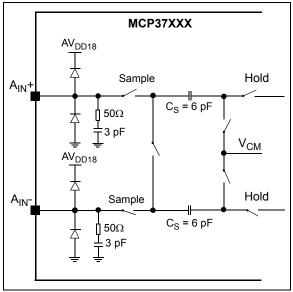

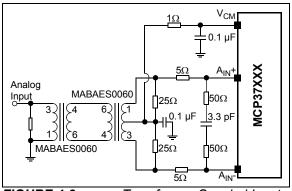

- Selectable Input Range: up to 2.975 V<sub>P-P</sub>

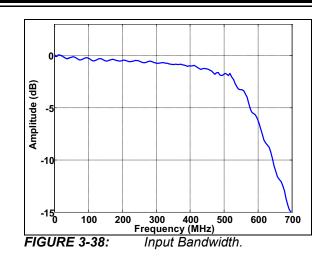

- Input Channel Bandwidth: 500 MHz

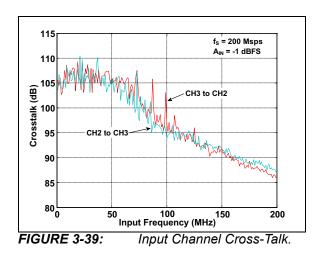

- Channel-to-Channel Crosstalk: >95 dB in Multi-Channel mode (Input = 15 MHz, -1 dBFS)

- Output Data Format:

- Parallel CMOS, DDR LVDS

- Serialized DDR LVDS (16-bit, octal-channel mode)

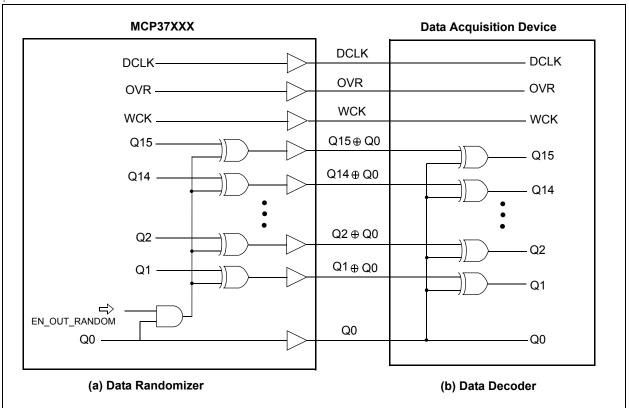

- · Optional Output Data Randomizer

- Digital Signal Post-Processing (DSPP) Options:

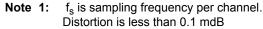

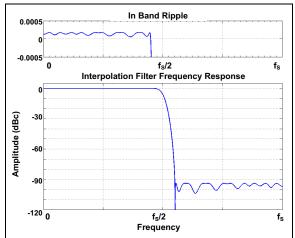

Decimation Filters for improved SNR

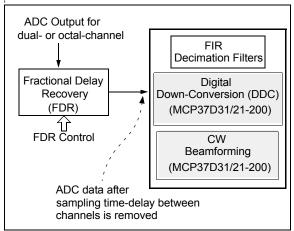

- Fractional Delay Recovery (FDR) for timedelay corrections in multi-channel operations (dual/octal-channel modes)

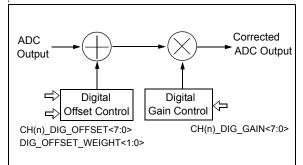

- Phase, Offset and Gain adjust of individual channels

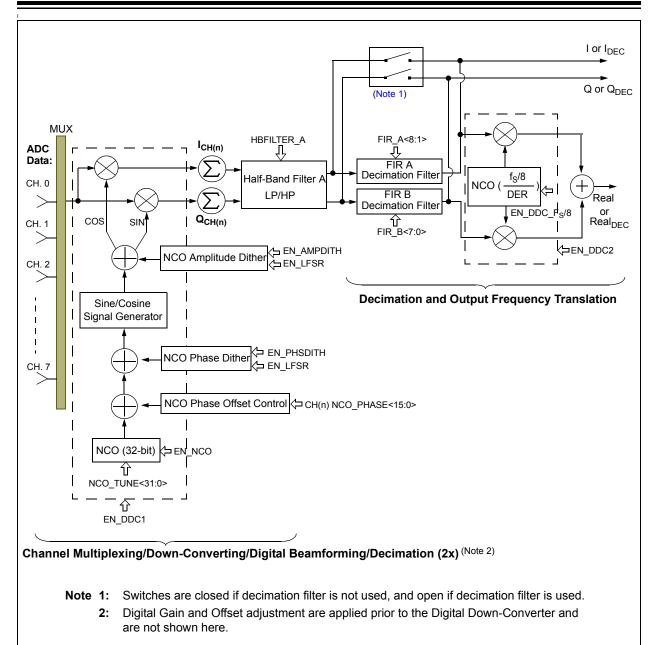

- Digital Down-Conversion (DDC) with I/Q or f<sub>S</sub>/8 output (MCP37D31/21-200)

- Continuous Wave Beamforming for octalchannel mode (MCP37D31/21-200)

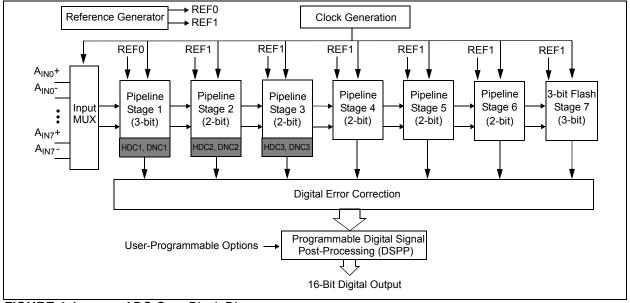

- Built-In ADC Linearity Calibration Algorithms:

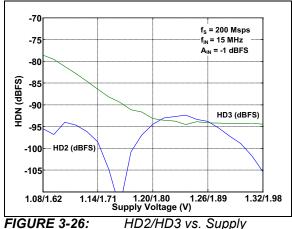

- Harmonic Distortion Correction (HDC)

- DAC Noise Cancellation (DNC)

- Dynamic Element Matching (DEM)

- Flash Error Calibration

- Serial Peripheral Interface (SPI)

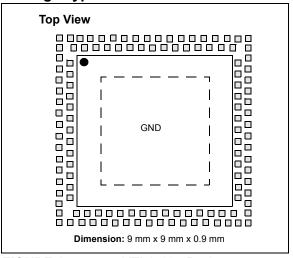

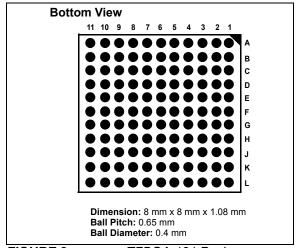

- · Package Options:

- VTLA-124 (9 mm x 9 mm x 0.9 mm)

- TFBGA-121 (8 mm x 8 mm x 1.08 mm)

- No external reference decoupling capacitor required for TFBGA Package

- Industrial Temperature Range: -40°C to +85°C

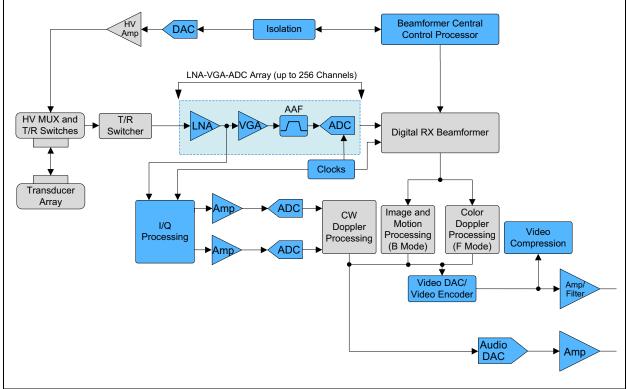

### **Typical Applications:**

- Communication Instruments

- Cellular Base Stations

- Radar

- · Ultrasound and Sonar Imaging

- · Scanners and Low-Power Portable Instruments

- · Industrial and Consumer Data Acquisition System

| Device | Offering | (Note | ): |

|--------|----------|-------|----|

|        |          |       |    |

| Part Number  | Sample Rate | Resolution | Digital Decimation | Digital<br>Down-Conversion | CW Beamforming |

|--------------|-------------|------------|--------------------|----------------------------|----------------|

| MCP37231-200 | 200 Msps    | 16         | Yes                | No                         | No             |

| MCP37221-200 | 200 Msps    | 14         | Yes                | No                         | No             |

| MCP37D31-200 | 200 Msps    | 16         | Yes                | Yes                        | Yes            |

| MCP37D21-200 | 200 Msps    | 14         | Yes                | Yes                        | Yes            |

**Note:** For TFBGA package, contact Microchip Technology Inc. for availability. The devices in the same package type are pin-compatible.

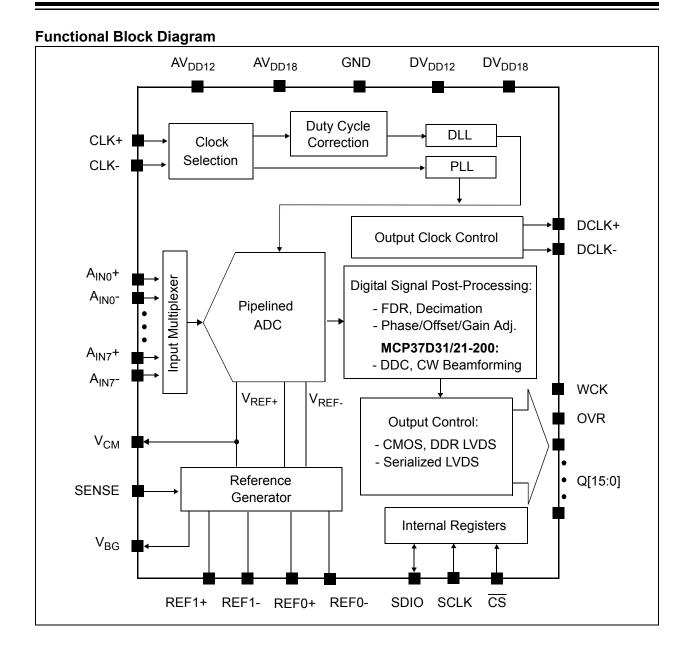

### **Description:**

The MCP37231/21-200 is Microchip's baseline 16-/14bit 200 Msps pipelined ADC family, featuring built-in high-order digital decimation filters, gain and offset adjustment per channel, and fractional delay recovery.

The MCP37D31/21-200 device family features a digital down-conversion and CW beamforming capability, in addition to the features offered by the MCP37231/21-200.

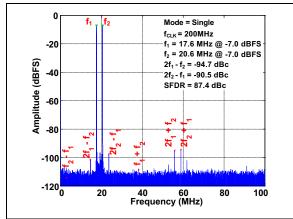

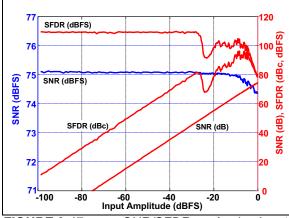

All devices feature harmonic distortion correction and DAC noise cancellation that enable high-performance specifications with SNR of greater than 74 dBFS, and SFDR of greater than 90 dBFS.

These A/D converters exhibit industry leading lowpower performance with only 490 mW operation while using the LVDS interface at 200 Msps. This superior low-power operation coupled with high dynamic performance makes these devices ideal for various high-performance, high-speed data acquisition systems including communications equipment, radar and portable instrumentation.

The output decimation filter option improves SNR performance up to 93.5 dBFS with the 512x decimation setting. The digital down-conversion option in conjunction with the decimation and quadrature output options offer great flexibility in digital communication system design, including cellular base-stations and narrow-band communications. Gain, phase and DC offset can be adjusted independently for each input channel, allowing for simplified implementation of CW beamforming and ultrasound Doppler imaging applications.

These devices can have up to eight differential input channels through an input MUX. The sampling rate is up to 200 Msps when a single channel is used, or 25 Msps per channel when all 8-input channels are used.

The differential full-scale analog input range is programmable up to 2.975  $V_{P-P}$ . The ADC output data can be coded in two's complement or offset binary representation, with or without the data randomizer option. The output data is available as full rate CMOS or double data rate (DDR) LVDS. Additionally, a serialized LVDS option is also available for the 16-bit octal-channel mode.

The device is available in a Pb-free VTLA-124 and TFBGA-121 packages. The device operates over the commercial temperature range of -40°C to +85°C.

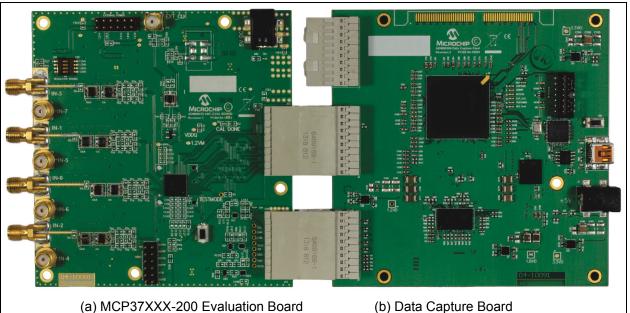

### Package Types

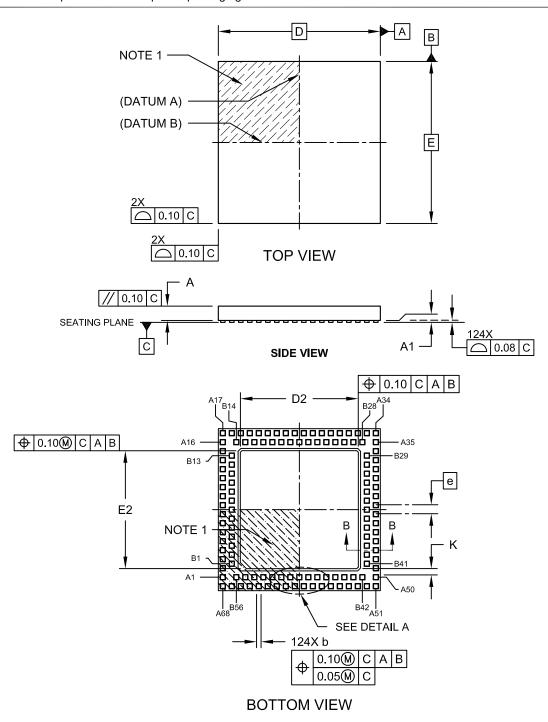

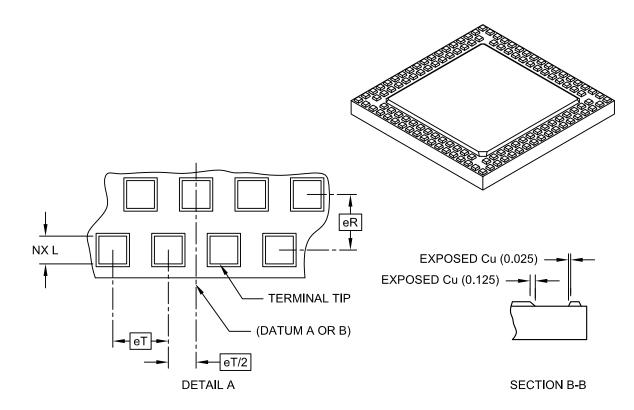

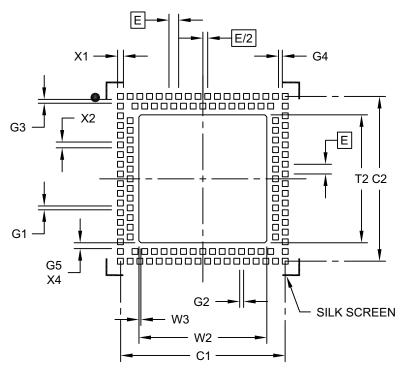

FIGURE 1:

VTLA-124 Package.

FIGURE 2: TFBGA-121 Package. (Contact Microchip Technology Inc. for availability)

NOTES:

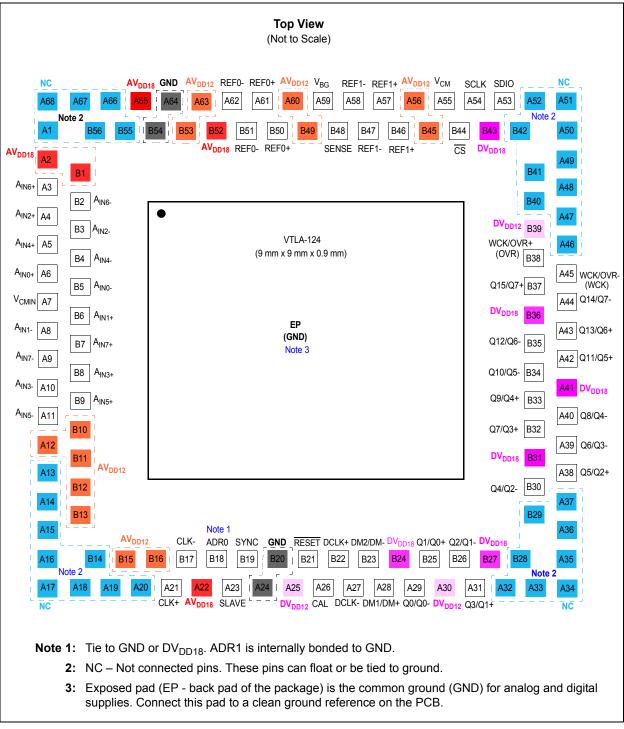

### 1.0 PACKAGE PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

**FIGURE 1-1:** VTLA-124 Package. See Table 1-1 for the pin descriptions and Table 1-3 for active and inactive ADC output pins for various ADC resolution modes.

| Pin No.                                                                     | Name               | I/O Type         | Description                                                                                                       |

|-----------------------------------------------------------------------------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------|

| Power Supply Pin                                                            | s                  |                  | ·                                                                                                                 |

| A2, A22, A65, B1,<br>B52                                                    | AV <sub>DD18</sub> | Supply           | Supply voltage input (1.8V) for analog section                                                                    |

| A12, A56, A60,<br>A63, B10, B11,<br>B12, B13, B15,<br>B16, B45, B49,<br>B53 | AV <sub>DD12</sub> |                  | Supply voltage input (1.2V) for analog section                                                                    |

| A25, A30, B39                                                               | DV <sub>DD12</sub> |                  | Supply voltage input (1.2V) for digital section                                                                   |

| A41, B24, B27,<br>B31, B36, B43                                             | DV <sub>DD18</sub> |                  | Supply voltage input (1.8V) for digital section and all digital I/O                                               |

| EP                                                                          | GND                |                  | Exposed pad: Common ground pin for digital and analog sections                                                    |

| ADC Analog Input                                                            | Pins               |                  | ·                                                                                                                 |

| A3                                                                          | A <sub>IN6+</sub>  | Analog           | Channel 6 differential analog input (+)                                                                           |

| B2                                                                          | A <sub>IN6-</sub>  | Input            | Channel 6 differential analog input (-)                                                                           |

| A4                                                                          | A <sub>IN2+</sub>  |                  | Channel 2 differential analog input (+)                                                                           |

| B3                                                                          | A <sub>IN2-</sub>  |                  | Channel 2 differential analog input (-)                                                                           |

| A5                                                                          | A <sub>IN4+</sub>  |                  | Channel 4 differential analog input (+)                                                                           |

| B4                                                                          | A <sub>IN4-</sub>  |                  | Channel 4 differential analog input (-)                                                                           |

| A6                                                                          | A <sub>IN0+</sub>  |                  | Channel 0 differential analog input (+)                                                                           |

| B5                                                                          | A <sub>IN0-</sub>  |                  | Channel 0 differential analog input (-)                                                                           |

| B6                                                                          | A <sub>IN1+</sub>  |                  | Channel 1 differential analog input (+)                                                                           |

| A8                                                                          | A <sub>IN1-</sub>  |                  | Channel 1 differential analog input (-)                                                                           |

| B7                                                                          | A <sub>IN7+</sub>  |                  | Channel 7 differential analog input (+)                                                                           |

| A9                                                                          | A <sub>IN7-</sub>  |                  | Channel 7 differential analog input (-)                                                                           |

| B8                                                                          | A <sub>IN3+</sub>  |                  | Channel 3 differential analog input (+)                                                                           |

| A10                                                                         | A <sub>IN3-</sub>  |                  | Channel 3 differential analog input (-)                                                                           |

| B9                                                                          | A <sub>IN5+</sub>  |                  | Channel 5 differential analog input (+)                                                                           |

| A11                                                                         | A <sub>IN5-</sub>  |                  | Channel 5 differential analog input (-)                                                                           |

| A21                                                                         | CLK+               |                  | Differential clock input (+)                                                                                      |

| B17                                                                         | CLK-               |                  | Differential clock input (-)                                                                                      |

| Reference Pins (N                                                           | ote 1)             |                  | ·                                                                                                                 |

| A57, B46                                                                    | REF1+              | Analog           | Differential reference 1 (+) voltage                                                                              |

| A58, B47                                                                    | REF1-              | Output           | Differential reference 1 (-) voltage                                                                              |

| A61, B50                                                                    | REF0+              |                  | Differential reference 0 (+) voltage                                                                              |

| A62, B51                                                                    | REF0-              |                  | Differential reference 0 (-) voltage                                                                              |

| SENSE, Bandgap                                                              | and Commo          | n Mode Volta     | ge Pins                                                                                                           |

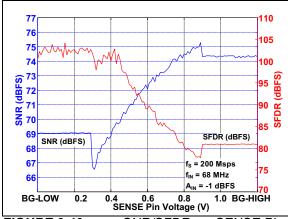

| B48                                                                         | SENSE              | Analog<br>Input  | Analog input full-scale range selection. See Table 4-2 for SENSE voltage settings.                                |

| A59                                                                         | $V_{BG}$           | Analog<br>Output | Internal bandgap output voltage<br>Connect a decoupling capacitor (2.2 μF)                                        |

| A7                                                                          | V <sub>CMIN</sub>  | Analog<br>Input  | Common-Mode voltage input for auto-calibration<br>Connect V <sub>CM</sub> voltage (Note 2)                        |

| A55                                                                         | $V_{CM}$           |                  | Common-Mode output voltage (900 mV) for analog input signal Connect a decoupling capacitor (0.1 $\mu$ F) (Note 3) |

### TABLE 1-1: PIN FUNCTION TABLE FOR VTLA-124

| TABLE 1-1:       |            | ON TABLE F               | OR VTLA-124 (CONTINUED)                                                                                                                             |

|------------------|------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.          | Name       | I/O Type                 | Description                                                                                                                                         |

| Digital I/O Pins |            | •                        |                                                                                                                                                     |

| B18              | ADR0       | Digital Input            | SPI address selection pin (A0 bit). Tie to GND or DV <sub>DD18</sub> . (Note 4)                                                                     |

| A23              | SLAVE      | -                        | Not used. Tie to GND.                                                                                                                               |

| B19              | SYNC       | Digital Input/<br>Output | Not used. Leave this pin floating.                                                                                                                  |

| B21              | RESET      | Digital Input            | Reset control input:<br>High: Normal operating mode<br>Low: Reset mode (Note 5)                                                                     |

| A26              | CAL        | Digital<br>Output        | Calibration status flag digital output:<br><b>High:</b> Calibration is complete<br><b>Low:</b> Calibration is not complete (Note 6)                 |

| B22              | DCLK+      |                          | LVDS: Differential digital clock output (+)<br>CMOS: Digital clock output (Note 7)                                                                  |

| A27              | DCLK-      |                          | LVDS: Differential digital clock output (-)<br>CMOS: Unused (leave floating)                                                                        |

| ADC Output Pins  | 6 (Note 8) |                          |                                                                                                                                                     |

| B23              | DM2/DM-    | Digital                  | 18-bit mode: Digital data output (last two LSB bits) (Note 9)                                                                                       |

| A28              | DM1/DM+    | Output                   | Other modes: Not used                                                                                                                               |

| A29              | Q0/Q0-     |                          | Digital data output: CMOS = Q0<br>DDR LVDS = Q0- (Even bit first), Q8- (MSB byte first)<br>Serialized LVDS = Q- for the last selected channel (n=8) |

| B25              | Q1/Q0+     |                          | Digital data output: CMOS = Q1<br>DDR LVDS = Q0+ (Even bit first), Q8+ (MSB byte first)<br>Serialized LVDS = Q+ for the last selected channel (n=8) |

| B26              | Q2/Q1-     |                          | Digital data output: CMOS = Q2<br>DDR LVDS = Q1- (Even bit first), Q9- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 7           |

| A31              | Q3/Q1+     |                          | Digital data output: CMOS = Q3<br>DDR LVDS = Q1+ (Even bit first), Q9+ (MSB byte first)<br>Serialized LVDS = Q+ for channel order (n) = 7           |

| B30              | Q4/Q2-     | -                        | Digital data output: CMOS = Q4<br>DDR LVDS = Q2- (Even bit first), Q10- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 6          |

| A38              | Q5/Q2+     |                          | Digital data output: CMOS = Q5<br>DDR LVDS = Q2+ (Even bit first), Q10+ (MSB byte first)<br>Serialized LVDS = Q+ for channel order (n) = 6          |

| A39              | Q6/Q3-     |                          | Digital data output: CMOS = Q6<br>DDR LVDS = Q3- (Even bit first), Q11- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 5          |

| B32              | Q7/Q3+     |                          | Digital data output: CMOS = Q7<br>DDR LVDS = Q3+ (Even bit first), Q11+ (MSB byte first)<br>Serialized LVDS = Q+ for channel order (n) = 5          |

| A40              | Q8/Q4-     |                          | Digital data output: CMOS = Q8<br>DDR LVDS = Q4- (Even bit first), Q12- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 4          |

| B33              | Q9/Q4+     |                          | Digital data output: CMOS = Q9<br>DDR LVDS = Q4+ (Even bit first), Q12+ (MSB byte first)<br>Serialized LVDS = Q+ for channel order (n) = 4          |

| B34              | Q10/Q5-    |                          | Digital data output: CMOS = Q10<br>DDR LVDS = Q5- (Even bit first), Q13- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 3         |

### TABLE 1-1: PIN FUNCTION TABLE FOR VTLA-124 (CONTINUED)

| Pin No.                                                                                               | Name              | I/O Type                 | Description                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A42                                                                                                   | Q11/Q5+           | Digital<br>Output        | Digital data output: CMOS = Q11<br>DDR LVDS = Q5+ (Even bit first), Q13+ (MSB byte first)<br>Serialized LVDS = Q+ for channel order (n) = 3              |

| B35                                                                                                   | Q12/Q6-           |                          | Digital data output: CMOS = Q12<br>DDR LVDS = Q6- (Even bit first), Q14- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 2              |

| A43                                                                                                   | Q13/Q6+           |                          | Digital data output: CMOS = Q13<br>DDR LVDS = Q6+ (Even bit first), Q14+ (MSB byte first)<br>Serialized LVDS = Q+ for channel order (n) = 2              |

| A44                                                                                                   | Q14/Q7-           |                          | Digital data output: CMOS = Q14<br>DDR LVDS = Q7- (Even bit first), Q15- (MSB byte first)<br>Serialized LVDS = Q- for the first selected channel (n = 1) |

| B37                                                                                                   | Q15/Q7+           |                          | Digital data output: CMOS = Q15<br>DDR LVDS = Q7+ (Even bit first), Q15+ (MSB byte first)<br>Serialized LVDS = Q+ for the first selected channel (n = 1) |

| B38                                                                                                   | WCK/OVR+<br>(OVR) |                          | WCK: Word clock sync digital output<br>OVR: Input over-range indication digital output (Note 10).                                                        |

| A45                                                                                                   | WCK/OVR-<br>(WCK) |                          |                                                                                                                                                          |

| SPI Interface Pins                                                                                    | ;                 |                          |                                                                                                                                                          |

| A53                                                                                                   | SDIO              | Digital Input/<br>Output | SPI data input/output                                                                                                                                    |

| A54                                                                                                   | SCLK              | Digital                  | SPI serial clock input                                                                                                                                   |

| B44                                                                                                   | CS                | Input                    | SPI Chip Select input                                                                                                                                    |

| Not Connected Pi                                                                                      | ins               |                          |                                                                                                                                                          |

| A1, A13 - A20,<br>A32 - A37, A46 -<br>A52, A66 - A68,<br>B14, B28, B29,<br>B40, B41, B42,<br>B55, B56 | NC                |                          | These pins can be tied to ground or left floating.                                                                                                       |

| Pins that need to                                                                                     | be grounded       |                          |                                                                                                                                                          |

| A24, A64,<br>B20, B54                                                                                 | GND               |                          | These pins are not supply pins, but need to be tied to ground.                                                                                           |

#### Notes:

- These pins are for the internal reference voltage outputs. They should not be driven. External decoupling circuits are required. See Section 4.5.3 "Decoupling Circuits for Internal Voltage Reference and Band Gap Output" for details.

- V<sub>CMIN</sub> is used for Auto-Calibration only. V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- should be tied together always. There should be no voltage difference between the two pins. Typically both V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- are tied to the V<sub>CM</sub> output pin together, but they can be tied to another common mode voltage if external V<sub>CM</sub> is used. This pin has High Z input in Shutdown, Standby and Reset modes.

- When V<sub>CM</sub> output is used for the common-mode voltage of analog inputs (i.e. by connecting to the center-tap of a balun), V<sub>CM</sub> pin should be decoupled with a 0.1 µF capacitor, and should be directly tied to V<sub>CMIN</sub>+ and V<sub>CMIN</sub>pins.

- 4. ADR1 (for A1 bit) is internally bonded to GND ('0'). If ADR0 is dynamically controlled, ADR0 must be held constant while CS is "Low".

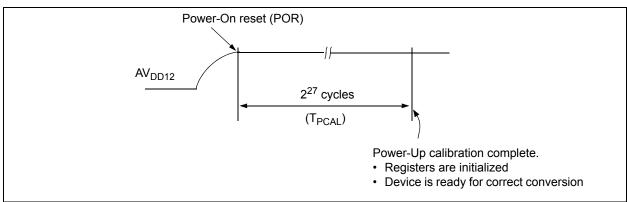

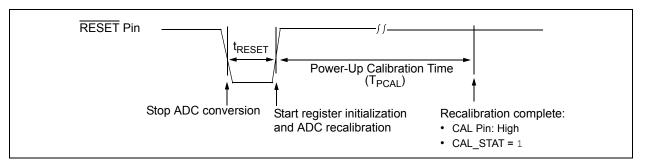

- 5. The device is in Reset mode while this pin stays "Low". On the rising edge of RESET, the device exits the Reset mode, initializes all internal user registers to default values, and begins power-up calibration.

- 6. CAL pin stays "Low" at power-up until the first power-up calibration is completed. When the first calibration has completed, this pin has "High" output. It stays "High" until the internal calibration is restarted by hardware or Soft Reset command. In Reset mode, this pin is "Low". In Standby and Shutdown modes, this pin will maintain the prior condition.

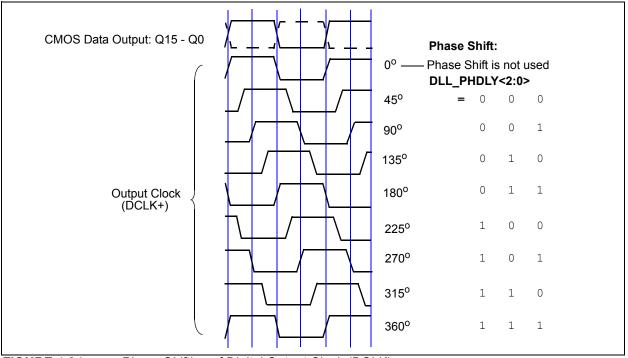

- The phase of DCLK relative to the data output bits may be adjusted depending on the operating mode. This is controlled differently depending on the configuration of the DSPP, PLL and/or DLL. See also Addresses 0x52, 0x64 and 0x6D (Registers 5-7, 5-21 and 5-27) for more details.

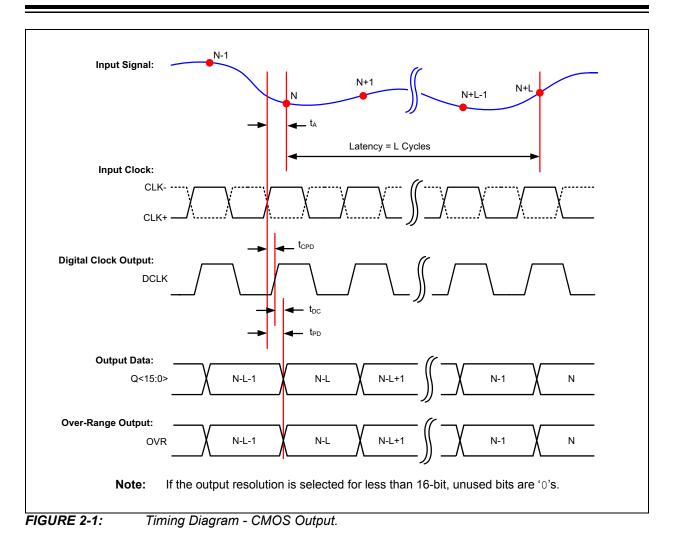

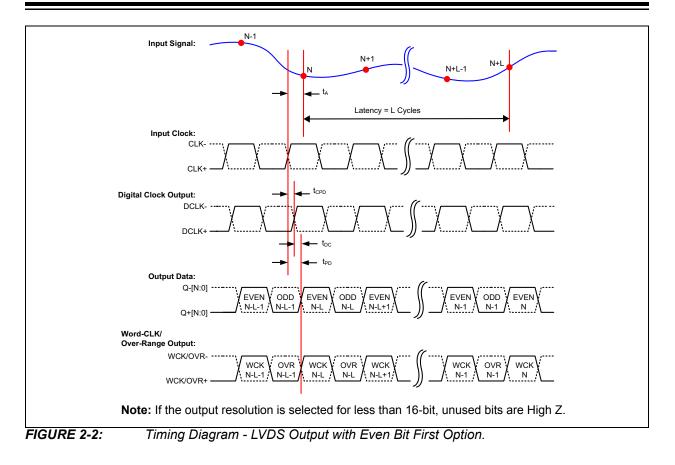

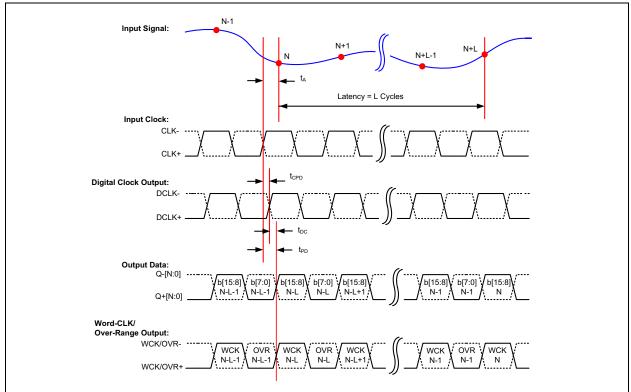

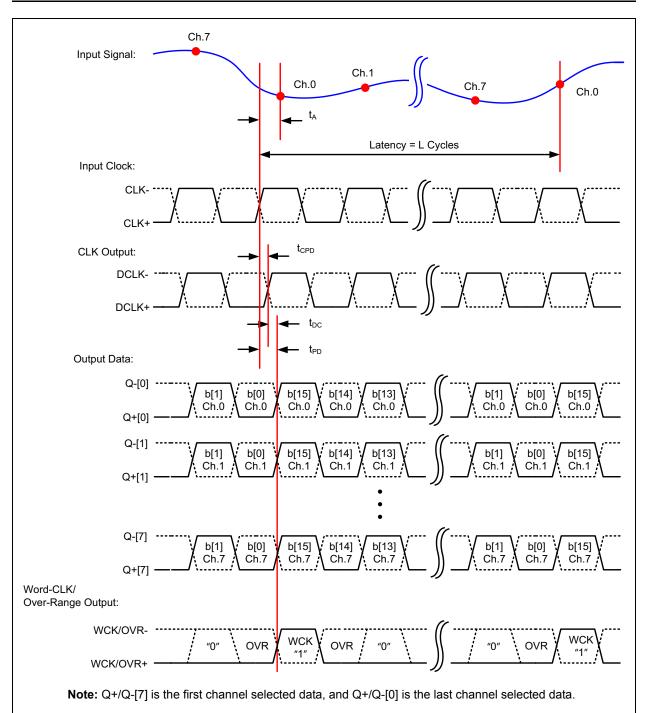

- 8. DDR LVDS: Two data bits are multiplexed onto each differential output pair. The output pins shown here are for the "Even bit first", which is the default setting of OUTPUT\_MODE<1:0> in Address 0x62 (Register 5-19). The even data bits (Q0, Q2, Q4, Q6, Q8, Q10, Q12, Q14) appear when DCLK+ is "High". The odd data bits (Q1, Q3, Q5, Q7, Q9, Q11, Q13, Q15) appear when DCLK+ is "Low". See Addresses 0x65 (Register 5-22) and 0x68 (Register 5-25) for output polarity control. See Figures 2-2 to 2-4 for LVDS output timing diagrams.

- Available for the MCP37231-200 and MCP37D31-200 devices only. Leave these pins floating (No Connect) if not used.

**18-bit mode:** DM1/DM+ and DM2/DM- are the last LSB bits. DM2/DM- is the LSB. In LVDS output, DM1/DM+ and DM2/DM- are the LSB pair. DM1/DM+ appears at the falling edge and DM2/DM- is at the rising edge of the DCLK+. Other than 18-bit mode: DM1/DM+ and DM2/DM- are High Z in LVDS mode.

- CMOS output mode: WCK/OVR+ is OVR and WCK/OVR- is WCK.

DDR LVDS output mode: The rising edge of DCLK+ is OVR and the falling edge is WCK.

OVR: OVR will be held "High" when analog input over-range is detected. Digital post-processing will cause OVR to assert early relative to the output data. See Figure 2-2 for LVDS timing of these bits.

WCK: Normally "Low". "High" while data from the first channel is sent out. In serialized LVDS (octal) output mode, the WCK output is asserted "High" on the MSB bit.

|   | 1                     | 2                     | 3                  | 4                  | 5                  | 6                             | 7                  | 8                     | 9                  | 10                  | 11                  |

|---|-----------------------|-----------------------|--------------------|--------------------|--------------------|-------------------------------|--------------------|-----------------------|--------------------|---------------------|---------------------|

| Α | SDIO                  | V <sub>CM</sub>       | REF1+              | REF1-              | V <sub>BG</sub>    | REF0+                         | REF0-              | GND                   | GND                | A <sub>IN4-</sub>   | A <sub>IN2+</sub>   |

| в | SCLK                  | cs                    | GND                | GND                | SENSE              | AV <sub>DD12</sub>            | AV <sub>DD12</sub> | AV <sub>DD18</sub>    | AV <sub>DD18</sub> | A <sub>IN4+</sub>   | A <sub>IN2-</sub>   |

| С | WCK/<br>OVR-<br>(WCK) | WCK/<br>OVR+<br>(OVR) | GND                | GND                | AV <sub>DD12</sub> | AV <sub>DD12</sub>            | AV <sub>DD12</sub> | GND                   | GND                | A <sub>IN6-</sub>   | A <sub>IN0+</sub>   |

| D | Q14/Q7-               | Q15/Q7+               | GND                | GND                | AV <sub>DD12</sub> | AV <sub>DD12</sub>            | AV <sub>DD12</sub> | GND                   | GND                | A <sub>IN6+</sub>   | A <sub>IN0-</sub>   |

| Е | Q12/Q6-               | Q13/Q6+               | GND                | GND                | AV <sub>DD12</sub> | AV <sub>DD12</sub>            | AV <sub>DD12</sub> | GND                   | GND                | A <sub>IN5+</sub>   | A <sub>IN1+</sub>   |

| F | Q10/Q5-               | Q11/Q5+               | DV <sub>DD18</sub> | DV <sub>DD18</sub> | AV <sub>DD12</sub> | AV <sub>DD12</sub>            | AV <sub>DD12</sub> | GND                   | GND                | A <sub>IN5-</sub>   | A <sub>IN1-</sub>   |

| G | Q8/Q4-                | Q9/Q4+                | DV <sub>DD18</sub> | DV <sub>DD18</sub> | GND                | GND                           | AV <sub>DD12</sub> | AV <sub>DD12</sub>    | GND                | A <sub>IN7-</sub>   | A <sub>IN3+</sub>   |

| н | Q6/Q3-                | Q7/Q3+                | DV <sub>DD12</sub> | DV <sub>DD12</sub> | GND                | GND                           | GND                | GND                   | GND                | A <sub>IN7+</sub>   | A <sub>IN3-</sub>   |

| J | Q4/Q2-                | Q5/Q2+                | DV <sub>DD12</sub> | DV <sub>DD12</sub> | GND                | GND                           | GND                | GND                   | GND                | V <sub>CMIN</sub> + | V <sub>CMIN</sub> - |

| Κ | Q2/Q1-                | Q3/Q1+                | DM1/DM+            | DCLK-              | CAL                | GND                           | SLAVE              | ADR0                  | ADR1               | GND                 | GND                 |

| L | Q0/Q0-                | Q1/Q0+                | DM2/DM-            | DCLK+              | RESET              | SYNC                          | GND                | CLK+                  | CLK-               | GND                 | AV <sub>DD18</sub>  |

|   |                       |                       |                    | All oth            |                    | Analog<br>Digital<br>Supply ` | Voltage            |                       |                    |                     |                     |

| 1 | 2:                    | Ball d                | imensio            | on: (a) E          | Ball Pito          |                               | 5 mm, (            | (b) Ball  <br>Ag 1.8% |                    | er = 0.4            | mm.                 |

**FIGURE 1-2:** TFBGA-121 Package. See Table 1-2 for the pin descriptions and Table 1-3 for active and inactive ADC output pins for various ADC resolution modes. Decoupling capacitors for reference pins and  $V_{BG}$  are embedded in the package.

### TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121

| Ball No. | Name               | I/O Type                 | Description                                                                                                                     |

|----------|--------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| A1       | SDIO               | Digital Input/<br>Output | SPI data input/output                                                                                                           |

| A2       | V <sub>CM</sub>    | Analog<br>Output         | Common-Mode output voltage (900 mV) for analog input signal Connect a decoupling capacitor (0.1 $\mu$ F) (Note 1)               |

| A3       | REF1+              | '                        | Differential reference voltage 1 (+/-). Decoupling capacitors are embedded in                                                   |

| A4       | REF1-              | -                        | the TFBGA package. Leave these pins floating.                                                                                   |

| A5       | V <sub>BG</sub>    |                          | Internal bandgap output voltage A decoupling capacitor (2.2 $\mu$ F) is embedded in the TFBGA package. Leave this pin floating. |

| A6       | REF0+              | -                        | Differential reference 0 (+/-) voltage. Decoupling capacitors are embedded ir                                                   |

| A7       | REF0-              |                          | the TFBGA package. Leave these pins floating.                                                                                   |

| A8<br>A9 | GND                | Supply                   | Common ground for analog and digital sections                                                                                   |

| A10      | A <sub>IN4-</sub>  | Analog Input             | Channel 4 differential analog input (-)                                                                                         |

| A11      | A <sub>IN2+</sub>  | -                        | Channel 2 differential analog input (+)                                                                                         |

| B1       | SCLK               | Digital Input            | SPI serial clock input                                                                                                          |

| B2       | CS                 | 1                        | SPI Chip Select input                                                                                                           |

| B3<br>B4 | GND                | Supply                   | Common ground for analog and digital sections                                                                                   |

| B5       | SENSE              | Analog<br>Input          | Analog input range selection. See Table 4-2 for SENSE voltage settings.                                                         |

| B6       | AV <sub>DD12</sub> | Supply                   | Supply voltage input (1.2V) for analog section                                                                                  |

| B7       |                    |                          |                                                                                                                                 |

| B8       | AV <sub>DD18</sub> |                          | Supply voltage input (1.8V) for analog section                                                                                  |

| B9       |                    |                          |                                                                                                                                 |

| B10      | A <sub>IN4+</sub>  | Analog Input             | Channel 4 differential analog input (+)                                                                                         |

| B11      | A <sub>IN2-</sub>  |                          | Channel 2 differential analog input (-)                                                                                         |

| C1       | WCK/OVR-           | Digital                  | WCK: Word clock sync digital output                                                                                             |

| C2       | (WCK)<br>WCK/OVR+  | Output                   | OVR: Input over-range indication digital output (Note 2)                                                                        |

|          | (OVR)              |                          |                                                                                                                                 |

| C3<br>C4 | GND                | Supply                   | Common ground for analog and digital sections                                                                                   |

| C5       | AV <sub>DD12</sub> | -                        | Supply voltage input (1.2V) for analog section                                                                                  |

| C6       |                    |                          |                                                                                                                                 |

| C7       |                    |                          |                                                                                                                                 |

| C8       | GND                |                          | Common ground pin for analog and digital sections                                                                               |

| C9       |                    |                          |                                                                                                                                 |

| C10      | A <sub>IN6-</sub>  | Analog Input             | Channel 6 differential analog input (-)                                                                                         |

| C11      | A <sub>IN0+</sub>  |                          | Channel 0 differential analog input (+)                                                                                         |

| D1       | Q14/Q7-            | Digital                  | Digital data output: (Note 3)                                                                                                   |

|          |                    | Output                   | CMOS = Q14<br>DDR LVDS = Q7- (Even bit first), Q15- (MSB byte first)                                                            |

|          |                    |                          | Serialized LVDS = Q- for the first selected channel (n = 1)                                                                     |

| D2       | Q15/Q7+            |                          | Digital data output: (Note 3)<br>CMOS = Q15<br>DDR LVDS = Q7+ (Even bit first), Q15+ (MSB byte first)                           |

| I        |                    |                          |                                                                                                                                 |

|          |                    |                          |                                                                                                                                 |

| D3       | GND                | Supply                   | Serialized LVDS = Q+ for the first selected channel (n = 1)<br>Common ground for analog and digital sections                    |

| TABLE 1- | 2: PIN F           | UNCTION TA        | ABLE FOR TFBGA-121 (CONTINUED)                                                                           |

|----------|--------------------|-------------------|----------------------------------------------------------------------------------------------------------|

| Ball No. | Name               | I/O Type          | Description                                                                                              |

| D5       | AV <sub>DD12</sub> | Supply            | Supply voltage input (1.2V) for analog section                                                           |

| D6       |                    |                   |                                                                                                          |

| D7       |                    |                   |                                                                                                          |

| D8       | GND                |                   | Common ground for analog and digital sections                                                            |

| D9       |                    |                   |                                                                                                          |

| D10      | A <sub>IN6+</sub>  | Analog Input      | Channel 6 differential analog input (+)                                                                  |

| D11      | A <sub>IN0-</sub>  | , and og input    | Channel 0 differential analog input (-)                                                                  |

| E1       | Q12/Q6-            | Digital           | Digital data output: (Note 3)                                                                            |

|          |                    | Output            | CMOS = Q12                                                                                               |

|          |                    |                   | DDR LVDS = Q6- (Even bit first), Q14- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 2 |

| E2       | Q13/Q6+            | _                 | Digital data output: (Note 3)                                                                            |

|          | Q10/Q01            |                   | CMOS = Q13                                                                                               |

|          |                    |                   | DDR LVDS = Q6+ (Even bit first), Q14+ (MSB byte first)                                                   |

|          |                    |                   | Serialized LVDS = $Q$ + for channel order (n) = 2                                                        |

| E3       | GND                | Supply            | Common ground for analog and digital sections                                                            |

| E4       |                    | _                 |                                                                                                          |

| E5       | AV <sub>DD12</sub> |                   | Supply voltage input (1.2V) for analog section                                                           |

| E6       | -                  |                   |                                                                                                          |

| E7<br>E8 | GND                | -                 | Common ground for analog and digital sections                                                            |

| E9       | GND                |                   |                                                                                                          |

| E10      | ۸                  |                   | Channel 5 differential analog input (+)                                                                  |

|          | A <sub>IN5+</sub>  | Analog Input      |                                                                                                          |

| E11      | A <sub>IN1+</sub>  | <b>D:</b> 11      | Channel 1 differential analog input (+)                                                                  |

| F1       | Q10/Q5-            | Digital<br>Output | Digital data output: (Note 3)<br>CMOS = Q10                                                              |

|          |                    | Output            | DDR LVDS = Q5- (Even bit first), Q13- (MSB byte first)                                                   |

|          |                    |                   | Serialized LVDS = Q- for channel order (n) = 3                                                           |

| F2       | Q11/Q5+            | -                 | Digital data output: (Note 3)                                                                            |

|          |                    |                   | CMOS = Q11                                                                                               |

|          |                    |                   | DDR LVDS = Q5+ (Even bit first), Q13+ (MSB byte first)                                                   |

| F3       |                    | Supply            | Serialized LVDS = Q+ for channel order (n) = 3<br>Supply voltage input (1.8V) for digital section.       |

| F3       | DV <sub>DD18</sub> | Supply            | All digital input pins are driven by the same DV <sub>DD18</sub> potential.                              |

| F5       | AV <sub>DD12</sub> | 1                 | Supply voltage input (1.2V) for analog section                                                           |

| F6       | 12                 |                   |                                                                                                          |

| F7       |                    |                   |                                                                                                          |

| F8       | GND                | 1                 | Common ground for analog and digital sections                                                            |

| F9       |                    |                   |                                                                                                          |

| F10      | A <sub>IN5-</sub>  |                   | Channel 5 differential analog input (-)                                                                  |

| F11      | A <sub>IN1-</sub>  | Analog Input      | Channel 1 differential analog input (-)                                                                  |

| G1       | Q8/Q4-             | Digital           | Digital data output: (Note 3)                                                                            |

|          |                    | Output            | CMOS = Q8                                                                                                |

|          |                    |                   | DDR LVDS = Q4- (Even bit first), Q12- (MSB byte first)                                                   |

| <u></u>  | 00/04:             | -                 | Serialized LVDS = Q- for channel order (n) = 4                                                           |

| G2       | Q9/Q4+             |                   | Digital data output: (Note 3)<br>CMOS = Q9                                                               |

|          |                    |                   | DDR LVDS = Q4+ (Even bit first), Q12+ (MSB byte first)                                                   |

|          |                    |                   | Serialized LVDS = $Q$ + for channel order (n) = 4                                                        |

| G3       | DV <sub>DD18</sub> | Supply            | Supply voltage input (1.8V) for digital section                                                          |

| G4       | 22.0               | _                 | All digital input pins are driven by the same DV <sub>DD18</sub> potential                               |

| G5       | GND                | 1                 | Common ground for analog and digital sections                                                            |

| G6       |                    |                   |                                                                                                          |

| TABLE 1- | 2: PIN F                               | UNCTION TA   | ABLE FOR TFBGA-121 (CONTINUED)                                                                                |

|----------|----------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------|

| Ball No. | Name                                   | I/O Type     | Description                                                                                                   |

| G7       | AV <sub>DD12</sub>                     | Supply       | Supply voltage input (1.2V) for analog section                                                                |

| G8       |                                        |              |                                                                                                               |

| G9       | GND                                    |              | Common ground for analog and digital sections                                                                 |

| G10      | A <sub>IN7-</sub>                      | Analog Input | Channel 7 differential analog input (-)                                                                       |

| G11      | A <sub>IN3+</sub>                      |              | Channel 3 differential analog input (+)                                                                       |

| H1       | Q6/Q3-                                 | Digital      | Digital data output: (Note 3)                                                                                 |

|          |                                        | Output       | CMOS = Q6<br>DDD LVDS = Q2 (Even bit first) Q11 (MSD byte first)                                              |

|          |                                        |              | DDR LVDS = Q3- (Even bit first), Q11- (MSB byte first)<br>Serialized LVDS = Q- for channel order (n) = 5      |

| H2       | Q7/Q3+                                 |              | Digital data output: (Note 3)                                                                                 |

|          |                                        |              | CMOS = Q7<br>DDR LVDS = Q3+ (Even bit first), Q11+ (MSB byte first)                                           |

|          |                                        |              | Serialized LVDS = $Q+$ for channel order (n) = 5                                                              |

| H3       | DV <sub>DD12</sub>                     | Supply       | Supply voltage input (1.2V) for digital section                                                               |

| H4       |                                        |              |                                                                                                               |

| H5       | GND                                    | _            | Common ground for analog and digital sections                                                                 |

| H6       |                                        |              |                                                                                                               |

| H7       |                                        |              |                                                                                                               |

| H8<br>H9 |                                        |              |                                                                                                               |

| H10      | Δ                                      |              | Channel 7 differential analog input (+)                                                                       |

| H11      | A <sub>IN7+</sub><br>A <sub>IN3-</sub> | Analog Input | Channel 3 differential analog input (-)                                                                       |

| J1       | Q4/Q2-                                 | Digital      | Digital data output: (Note 3)                                                                                 |

| 51       | Q <del>,</del> , QZ-                   | Output       | CMOS = Q4                                                                                                     |

|          |                                        |              | DDR LVDS = Q2- (Even bit first), Q10- (MSB byte first)                                                        |

|          |                                        | _            | Serialized LVDS = Q- for channel order (n) = 6                                                                |

| J2       | Q5/Q2+                                 |              | Digital data output: (Note 3)<br>CMOS = Q5                                                                    |

|          |                                        |              | DDR LVDS = Q2+ (Even bit first), Q10+ (MSB byte first)                                                        |

|          |                                        |              | Serialized LVDS = $Q$ + for channel order (n) = 6                                                             |

| J3       | DV <sub>DD12</sub>                     | Supply       | DC supply voltage input pin for digital section (1.2V)                                                        |

| J4       |                                        |              |                                                                                                               |

| J5       | GND                                    |              | Common ground for analog and digital sections                                                                 |

| J6<br>J7 |                                        |              |                                                                                                               |

| J8       |                                        |              |                                                                                                               |

| J9       |                                        |              |                                                                                                               |

| J10      | V <sub>CMIN+</sub>                     | Analog Input |                                                                                                               |

| J11      | V <sub>CMIN</sub> -                    | -            | These two pins should be tied together and connected to $V_{CM}$ voltage.                                     |

| K1       | Q2/Q1-                                 | Digital      | Digital data output: (Note 3)                                                                                 |

|          |                                        | Output       | CMOS = Q2                                                                                                     |

|          |                                        |              | DDR LVDS = Q1- (Even bit first), Q9- (MSB byte first)                                                         |

| К2       | Q3/Q1+                                 | -            | Serialized LVDS = Q- for channel order (n) = 7<br>Digital data output: (Note 3)                               |

| 112      |                                        |              | CMOS = Q3                                                                                                     |

|          |                                        |              | DDR LVDS = Q1+ (Even bit first), Q9+ (MSB byte first)                                                         |

|          |                                        |              | Serialized LVDS = Q+ for channel order (n) = 7                                                                |

| K3       | DM1/DM+                                |              | <b>18-bit mode:</b> Digital data output. DM1 and DM2 are the last two LSB bits (Note 5) Other modes: Not used |

| K4       | DCLK-                                  |              | LVDS: Differential digital clock output (-)                                                                   |

|          |                                        |              | CMOS: Unused (leave floating)                                                                                 |

### TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121 (CONTINUED)

| IABLE 1- |                    | 1              | ABLE FOR IFBGA-121 (CONTINUED)                                                   |

|----------|--------------------|----------------|----------------------------------------------------------------------------------|

| Ball No. | Name               | I/O Type       | Description                                                                      |

| K5       | CAL                | Digital        | Calibration status flag digital output (Note 6):                                 |

|          |                    | Output         | High: Calibration is complete                                                    |

|          |                    |                | Low: Calibration is not complete                                                 |

| K6       | GND                | Supply         | Common ground pin for analog and digital sections                                |

| K7       | SLAVE              | Digital Input  | Not used. Tie this pin to GND                                                    |

| K8       | ADR0               |                | SPI address selection pin (A0 bit). Tie to GND or DVDD18 (Note 7)                |

| K9       | ADR1               |                | SPI address selection pin (A1 bit). Tie to GND or DVDD18 (Note 7)                |

| K10      | GND                | Supply         | Common ground for analog and digital sections                                    |

| K11      |                    |                |                                                                                  |

| L1       | Q0/Q0-             | Digital        | Digital data output: (Note 3)                                                    |

|          |                    | Output         | CMOS = Q0                                                                        |

|          |                    |                | DDR LVDS = Q0- (Even bit first), Q8- (MSB byte first)                            |

|          |                    |                | Serialized LVDS = Q- for the last selected channel (n=8)                         |

| L2       | Q1/Q0+             |                | Digital data output: (Note 8)                                                    |

|          |                    |                | CMOS = Q1                                                                        |

|          |                    |                | DDR LVDS = Q0+ (Even bit first), Q8+ (MSB byte first)                            |

|          |                    | _              | Serialized LVDS = Q+ for the last selected channel (n=8)                         |

| L3       | DM2/DM-            |                | 18-bit mode: Digital data output. DM1 and DM2 are the last two LSB bits (Note 5) |

|          |                    | _              | Other modes: Not used                                                            |

| L4       | DCLK+              |                | LVDS: Differential digital clock output (+)                                      |

|          |                    |                | CMOS: Digital clock output (Note 8)                                              |

| L5       | RESET              | Digital Input  | Reset control input:                                                             |

|          |                    |                | High: Normal operating mode                                                      |

|          |                    |                | Low: Reset mode (Note 9)                                                         |

| L6       | SYNC               | Digital Input/ | Not used. Leave this pin floating                                                |

|          |                    | Output         |                                                                                  |

| L7       | GND                | Supply         | Common ground for analog and digital sections                                    |

| L8       | CLK+               | Analog Input   | Differential clock input (+)                                                     |

| L9       | CLK-               |                | Differential clock input (-)                                                     |

| L10      | GND                | Supply         | Common ground for analog and digital sections                                    |

| L11      | AV <sub>DD18</sub> | Analog Input   | Supply voltage input (1.8V) for analog section                                   |

### TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121 (CONTINUED)

#### Notes:

- When V<sub>CM</sub> output is used for the common-mode voltage of analog inputs (i.e. by connecting to the center-tap of a balun), V<sub>CM</sub> pin should be decoupled with a 0.1 μF capacitor, and should be directly tied to V<sub>CMIN</sub>+ and V<sub>CMIN</sub>pins.

- 2. CMOS output mode: WCK/OVR- is WCK and WCK/OVR+ is OVR.

DDR LVDS output mode: The rising edge of DCLK+ is OVR and the falling edge is WCK.

OVR: OVR will be held "High" when analog input over-range is detected. Digital post-processing will cause OVR to assert early relative to the output data. See Figure 2-2 for LVDS timing of these bits.

WCK: Normally "Low". "High" while data from the first channel is sent out. In serialized LVDS (octal) output mode, the WCK output is asserted "High" on the MSB bit.

- 3. DDR LVDS: Two data bits are multiplexed onto each differential output pair. The output pins shown here are for the "Even bit first", which is the default setting of OUTPUT\_MODE<1:0> in Address 0x62 (Register 5-19). The even data bits (Q0, Q2, Q4, Q6, Q8, Q10, Q12, Q14) appear when DCLK+ is "High". The odd data bits (Q1, Q3, Q5, Q7, Q9, Q11, Q13, Q15) appear when DCLK+ is "Low". See Addresses 0x65 (Register 5-22) and 0x68 (Register 5-25) for output polarity control. See Figures 2-2 to 2-4 for LVDS output timing diagrams.

- 4. V<sub>CMIN</sub> is used for Auto-Calibration only. V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- should be tied together always. There should be no voltage difference between the two pins. Typically both V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- are tied to the V<sub>CM</sub> output pin together, but they can be tied to another common mode voltage if external V<sub>CM</sub> is used. This pin has High Z input in Shutdown, Standby and Reset modes.

- Available for the MCP37231-200 and MCP37D31-200 devices only. Leave these pins floating (No Connect) if not used.

**18-bit mode:** DM1/DM+ and DM2/DM- are the last LSB bits. DM2/DM- is the LSB. In LVDS output, DM1/DM+ and DM2/DM- are the LSB pair. DM1/DM+ appears at the falling edge and DM2/DM- is at the rising edge of the DCLK+.

Other than 18-bit mode: DM1/DM+ and DM2/DM- are High Z in LVDS mode.

- 6. CAL pin stays "Low" at power-up until the first power-up calibration is completed. When the first calibration has completed, this pin has "High" output. It stays "High" until the internal calibration is restarted by hardware or Soft Reset command. In Reset mode, this pin is "Low". In Standby and Shutdown modes this pin will maintain the prior condition.

- 7. If the SPI address is dynamically controlled, the Address pin must be held constant while CS is "Low".

- 8. The phase of DCLK relative to the data output bits may be adjusted depending on the operating mode. This is controlled differently depending on the configuration of the digital post-processing, PLL and/or DLL. See also Addresses 0x52, 0x64 and 0x6D (Registers 5-7, 5-21 and 5-27) for more details.

- 9. The device is in Reset mode while this pin stays "Low". On the rising edge of RESET, the device exits the Reset mode, initializes all internal user registers to default values, and begins power-up calibration.

### TABLE 1-3: DATA OUTPUT PINS FOR EACH RESOLUTION OPTION

| ADC                        |             | Output Pin Name                                       |             |             |             |             |            |            |            |            |            |            |            |            |            |            |             |             |

|----------------------------|-------------|-------------------------------------------------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------------|-------------|

| Resolution                 | Q15/<br>Q7+ | Q14/<br>Q7-                                           | Q13/<br>Q6+ | Q12/<br>Q6- | Q11/<br>Q5+ | Q10/<br>Q5- | Q9/<br>Q4+ | Q8/<br>Q4- | Q7/<br>Q3+ | Q6/<br>Q3- | Q5/<br>Q2+ | Q4/<br>Q2- | Q3/<br>Q1+ | Q2/<br>Q1- | Q1/<br>Q0+ | Q0/<br>Q0- | DM1/<br>DM+ | DM2<br>/DM- |

| 18-bit mode                |             | Q15 pin is MSB (bit 17), and DM2 is LSB (bit 0)       |             |             |             |             |            |            |            |            |            |            |            |            |            |            |             |             |

| 16-bit mode                |             | Q15 pin is MSB, and Q0 is LSB Not used (1)            |             |             |             |             |            |            |            |            |            |            |            |            |            |            |             |             |

| 14-bit mode <sup>(2)</sup> |             | Q15 pin is MSB, and Q2 is LSB Not used <sup>(1)</sup> |             |             |             |             |            |            |            |            |            |            |            |            |            |            |             |             |

| 12-bit mode                |             | Q15 pin is MSB, and Q4 is LSB Not used <sup>(1)</sup> |             |             |             |             |            |            |            |            |            |            |            |            |            |            |             |             |

| 10-bit mode                |             | Q15 pin is MSB, and Q6 is LSB Not used <sup>(1)</sup> |             |             |             |             |            |            |            |            |            |            |            |            |            |            |             |             |

**Note 1:** Output condition at "not-used" output pin:

'0' in CMOS mode. These pins can be grounded or left floating.

High Z state in LVDS mode.

2: The MCP37221-200 and MCP37D21-200 devices have 14-bit mode option only, while the MCP37231-200 and MCP37D31-200 have all listed resolution options.

NOTES:

### 2.0 ELECTRICAL SPECIFICATIONS

### 2.1 Absolute Maximum Ratings†

| Analog and Digital Supply Voltage (AV <sub>DD12</sub> , DV <sub>DD12</sub> )0.3V to 1.32V |

|-------------------------------------------------------------------------------------------|

| Analog and Digital Supply Voltage (AV <sub>DD18</sub> , DV <sub>DD18</sub> )              |

| -0.3V to 1.98V                                                                            |

| All inputs and outputs w.r.t GND–0.3V to AV_{DD18} + 0.3V                                 |

| Differential Input Voltage  AV <sub>DD18</sub> - GND                                      |

| Current at Input Pins±2 mA                                                                |

| Current at Output and Supply Pins±250 mA                                                  |

| Storage Temperature65°C to +150°C                                                         |

| Ambient Temp. with power applied (T <sub>A</sub> )55°C to +125°C                          |

| Maximum Junction Temperature (T <sub>J</sub> )+150°C                                      |

| ESD protection on all pins2 kV HBM                                                        |

| Solder Reflow Profile                                                                     |

**Notice†**: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 2.2 Electrical Specifications

### TABLE 2-1: ELECTRICAL CHARACTERISTICS

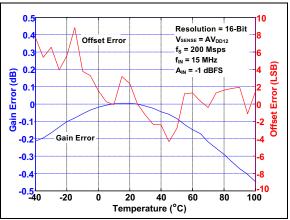

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}$ C to +85°C, AV<sub>DD18</sub> = DV<sub>DD18</sub> = 1.8V, AV<sub>DD12</sub> = DV<sub>DD12</sub> = 1.2V, GND = 0V, SENSE = AV<sub>DD12</sub>, Single-channel mode, Differential Analog Input (A<sub>IN</sub>) = Sine wave with amplitude of -1 dBFS,  $f_{IN} = 70$  MHz, Clock Input = 200 MHz,  $f_S = 200$  Msps (ADC Core), Resolution = 16-bit, PLL and decimation filters are disabled, Output load: CMOS data pin = 10 pF, LVDS = 100 $\Omega$  termination, LVDS driver current setting = 3.5 mA, DCLK\_PHDLY\_DEC<2:0> = 000, +25°C is applied for typical value.

| Parameters                                 | Sym.                     | Min. | Тур.        | Max.     | Units | Conditions                                  |

|--------------------------------------------|--------------------------|------|-------------|----------|-------|---------------------------------------------|

| Power Supply Requirem                      | ents                     |      |             |          |       | ·                                           |

| Analog Supply Voltage                      | AV <sub>DD18</sub>       | 1.71 | 1.8         | 1.89     | V     |                                             |

|                                            | AV <sub>DD12</sub>       | 1.14 | 1.2         | 1.26     | V     |                                             |

| Digital Supply Voltage                     | DV <sub>DD18</sub>       | 1.71 | 1.8         | 1.89     | V     | Note 1                                      |

|                                            | DV <sub>DD12</sub>       | 1.14 | 1.2         | 1.26     | V     |                                             |

| Analog Supply Current                      |                          |      |             |          |       |                                             |

| Analog Supply Current                      | I <sub>DD_A18</sub>      | —    | 27          | 46       | mA    | at AV <sub>DD18</sub> Pin                   |

| during Conversion                          | I <sub>DD_A12</sub>      |      | 185         | 252      | mA    | at AV <sub>DD12</sub> Pin                   |

| Digital Supply Current                     |                          |      |             |          |       |                                             |

| Digital Supply Current during Conversion   | I <sub>DD_D12</sub>      | _    | 97          | 226      | mA    | at DV <sub>DD12</sub> Pin                   |

| Digital I/O Current in<br>CMOS Output Mode | I <sub>DD_D18</sub>      |      | 27          | —        | mA    | at DV <sub>DD18</sub> Pin<br>DCLK = 100 MHz |

| Digital I/O Current in                     | I <sub>DD D18</sub>      | Ν    | leasured at | <u>.</u> | +     |                                             |

| LVDS Mode                                  |                          |      | 55          | 81       | mA    | 3.5 mA mode                                 |

|                                            |                          | —    | 39          | —        | mA    | 1.8 mA mode                                 |

|                                            |                          |      | 69          |          |       | 5.4 mA mode                                 |

| Supply Current during P                    | ower Saving Mo           | odes |             |          |       |                                             |

| During Standby Mode                        | I <sub>STANDBY_AN</sub>  |      | 21          | —        | mA    | Address 0x00<4:3> = 1, 1                    |

|                                            | I <sub>STANDBY_DIG</sub> | _    | 41          | _        |       | (Note 2)                                    |

| During Shutdown Mode                       | I <sub>DD_SHDN</sub>     | —    | 25          | _        | mA    | Address 0x00<7,0> = 1,1<br>(Note 3)         |

### TABLE 2-1: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}$ C to +85°C, AV<sub>DD18</sub> = DV<sub>DD18</sub> = 1.8V, AV<sub>DD12</sub> = DV<sub>DD12</sub> = 1.2V, GND = 0V, SENSE = AV<sub>DD12</sub>, Single-channel mode, Differential Analog Input (A<sub>IN</sub>) = Sine wave with amplitude of -1 dBFS,  $f_{IN} = 70$  MHz, Clock Input = 200 MHz,  $f_S = 200$  Msps (ADC Core), Resolution = 16-bit, PLL and decimation filters are disabled, Output load: CMOS data pin = 10 pF, LVDS = 100 $\Omega$  termination, LVDS driver current setting = 3.5 mA, DCLK\_PHDLY\_DEC<2:0> = 000, +25°C is applied for typical value.

| Parameters                                                            | Sym.                            | Min. | Тур.                            | Max.        | Units            | Conditions                                                          |

|-----------------------------------------------------------------------|---------------------------------|------|---------------------------------|-------------|------------------|---------------------------------------------------------------------|

| PLL Circuit                                                           |                                 |      | 1                               |             |                  |                                                                     |

| PLL Circuit Current                                                   | I <sub>DD_PLL</sub>             | -    | 21                              | _           | mA               | PLL enabled. Included in<br>analog supply current<br>specification. |

| Total Power Dissipation (                                             | lote 4)                         |      | 1                               |             | 1                |                                                                     |

| Power Dissipation<br>during conversion,<br>excluding digital I/O      | P <sub>DISS_ADC</sub>           | _    | 387                             | 689.2       | mW               |                                                                     |

| Total Power Dissipation<br>during conversion with<br>CMOS output mode | P <sub>DISS_CMOS</sub>          | —    | 436                             | —           | mW               | f <sub>S</sub> = 200 Msps,<br>DCLK = 100 MHz                        |

| Total Power Dissipation                                               | P <sub>DISS_LVDS</sub>          |      | 486                             | 842.3       | mW               | 3.5 mA mode                                                         |

| during conversion with                                                | _                               | —    | 457                             | _           |                  | 1.8 mA mode                                                         |

| LVDS output mode                                                      |                                 |      | 511                             |             |                  | 5.4 mA mode                                                         |

| During Standby Mode                                                   | P <sub>DISS_</sub> -<br>standby | —    | 80.4                            | —           | mW               | Address 0x00<4:3> = 1, 1 (Note 2)                                   |

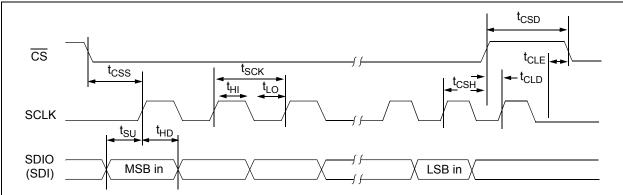

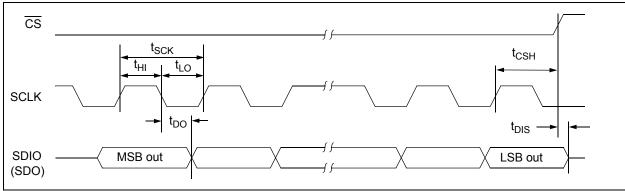

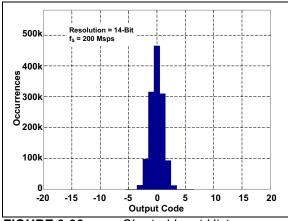

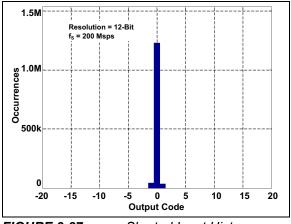

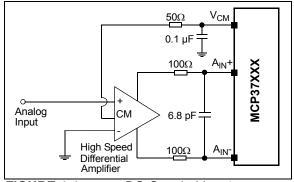

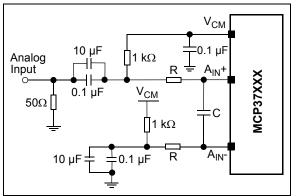

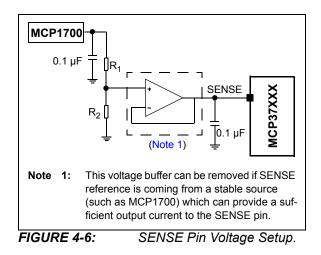

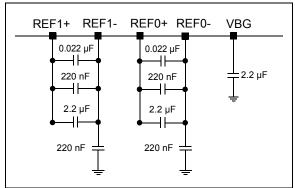

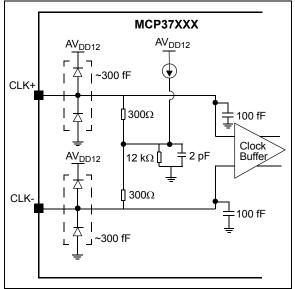

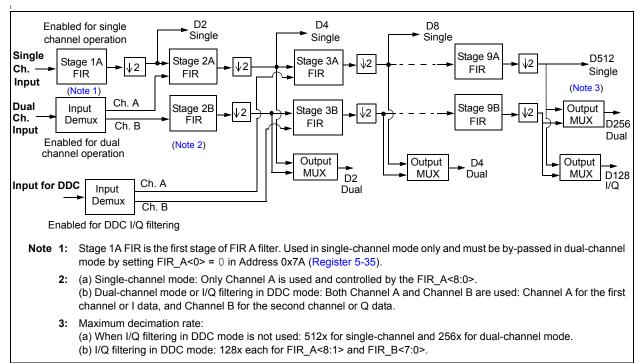

| During Shutdown Mode                                                  | P <sub>DISS_SHDN</sub>          | —    | 33                              | —           | mW               | Address 0x00<7,0> = 1, 1 (Note 3)                                   |